Развитие микроэлектроники в начале 60-х гг. прошлого века привело к созданию интегральных микросхем, которые представляют собой функциональные узлы электронной аппаратуры, все компоненты и соединительные проводники которой изготавливаются в объеме или на поверхности полупроводникового кристалла в едином технологическом цикле. В первых интегральных микросхемах (ИМС) на кристалле изготавливались логические элементы, реализующие элементарные логические функции.

По мере совершенствования цифровой техники и микроэлектронных технологий стало возможным размещать на полупроводниковых (ПП) кристаллах сначала сто, потом тысячу, а затем десятки миллионов ПП элементов.

Сложность ИМС принято оценивать количеством размешенных на кристалле логических элементов. По этому критерию цифровые ИМС подразделяются на следующие уровни:

МИС – малые интегральные схемы, малого уровня сложности (до десяти логических элементов);

СИС – интегральные схемы средней сложности (до ста логических элементов);

БИС – большие интегральные схемы (до тысячи логических элементов);

СБИС – сверхбольшие интегральные схемы (до десяти тысяч элементов);

УБИС – ультра большие (до ста тысяч элементов).

С увеличением плотности компоновки логических элементов на кристалле обострилась проблема экономической обоснованности того, какие функциональные узлы целесообразно реализовывать в интегральном исполнении с тем, чтобы это было экономически выгодно. Естественным выходом в этих условиях стало изготовление заказных БИС, которые разрабатывались каждый раз специально для конкретного применения. Однако потребление таких ИМС постоянно снижалось, поскольку специализация подобных БИС привела к ограничению их области применения. По этой причине были разработаны БИС, программируемые пользователем, в структуру которых на этапе производства вводят избыточное количество ПП элементов и связей, часть которых в процессе программирования в дальнейшем разрушается.

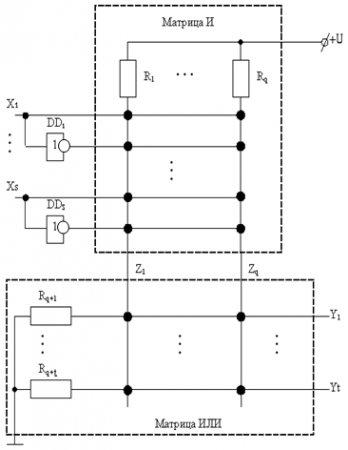

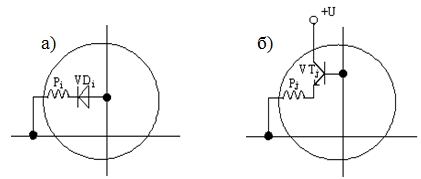

К числу таких ИМС относят двухуровневые программируемые логические матрицы (ПЛМ). Схема электрическая функциональная незапрограммированной ПЛМ показана на рисунке 1.5. Каждая из матриц представляет собой систему ортогональных проводников, в местах пересечений которых установлены ПП элементы. В матрице "И" этим элементом является диод (рисунок 1.6а), а в матрице "ИЛИ" − триод или транзистор (рисунок 1.6б). С помощью диодов и резисторов нагрузки Rl...Rq на промежуточных шинах Zl...Zq формируются элементарные конъюнкции над любыми значениями входных переменных. На шинах Y1...Yt формируются элементарные дизъюнкции над сигналами, поступающими по шинам Zl...Zq. Дизъюнкции реализуются с помощью транзисторов и соответствующих резисторов нагрузки Rq+1...Rq+t.

Рисунок 1.6 - Подключение ПП элемента в узлах ПЛМ:

а) диод, б) триод (транзистор)

При изображении схемы электрической функциональной ПЛМ разрешается не вычерчивать полупроводниковые структуры, наличие которых обеспечивает реализацию заданных логических функций в СДНФ. По этой причине на рисунке 1.5 отсутствуют изображения диодов и триодов.

Программирование двухуровневых ПЛМ заключается в удалении или изоляции тех ПП-элементов, которые являются ненужными. В этом случае в местах установки ПП-элементов ставятся специальные метки (например, черная точка, как на рисунке 1.5, или крестик).

Как было отмечено, элементы БП реализуются на базе триггеров. Триггеры - это устройства, которые могут находиться в одном из двух устойчивых состояниях и переходить из одного состояния в другое под воздействием входных сигналов.

В общем случае триггер можно представить как nk – полюсник, то есть триггер представляет собой устройство, которое имеет совокупность управляющих входов n и/или один/несколько выходов k. Один из выходов принято называть − прямым, другой − инверсным.

Состояние триггера по умолчанию принято воспринимать на прямом выходе. Информационными входами могут быть: S - (set) установка в единицу, R - (reset) установка в ноль, Т - (time) счет, J - тождественно S, К - тождественно R, D - (delay). К управляющим входам относят: С - (clock) вход синхронизации

Основными типами триггерных схем являются: асинхронный RS-триггер, синхронный двухтактный RS-триггер, D-триггер, Т-триггер, JK-триггер и Триггер Шмита. Также встречаются комбинированные триггеры, триггеры с входной логикой, комбинированные триггеры с входной логикой и т.д. Кроме того, триггеры бывают однотактные и двухтактные.

В данном курсовом проекте для построения схемы электрической функциональной синхронного УА предполагается использовать комбинированный синхронный двухтактный JK-триггер.