На основе проведенного кодирования структурных состояний ai синхронного УА и заданного условиями курсового проекта комбинированного синхронного двухтактного JK-триггера детализируем структурную схему УА, в частности, его блок памяти.

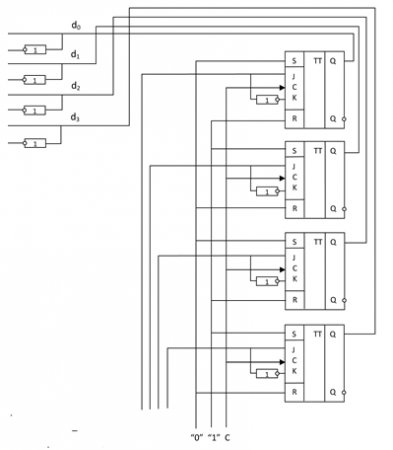

Как было рассчитано выше, блок памяти синхронного УА будет состоять из четырех JK-триггерных схем. В начальный момент дискретного времени сигналом начальной установки «Н.У.» на входы S триггеров подается структурный код, соответствующий начальному внутреннему состоянию a1, то есть d0=0, d1=1, d2=0, d3=1. В следующий момент дискретного времени, задаваемый синхронизирующим сигналом Sync, подаваемым на синхровходы JK-триггеров, этот структурный код поступит в ЛП и работа УА начнется.

В процессе детализации необходимо помнить, что синхронные JK-триггеры могут, в частности, быть преобразованы в D-триггеры, схема подключения которых значительно упрощается. Для такого преобразования необходимо синхронизируемые входы JK-триггера соединить, как показано ниже.

Рисунок 2.3 - Пример преобразования синхронного JK-триггера в синхронный D-триггер

С учетом такого преобразования, результат детализации БП синхронного УА представлен на рисунке 2.4.